开关电源芯片的失效分析与可靠性研究

2024-10-27 重庆开荒保洁

:随着科技的快速的提升,电器设备的使用愈来愈普遍,功能也慢慢变得强大,体积也慢慢变得小,导致了对电源模块要求在持续不断的增加。开关芯片在应用中失效,经分析为电路设计本身差,导致开关芯片失效。本文通过增加放电与限流贴片电阻,对电路设计优化更改,使电路工作

现代电子设备对电源模块的工作效率、体积以及安全要求等技术性能指标要求慢慢的升高,开关电源电路凭借良好的性能在电子设备中得到了广泛的应用。开关芯片作为开关电源电路的重要组成器件,决定了开关电源的质量。开关芯片在各种设备电源模块、以及家用电器均有使用。随开关电源电路的大量使用,售后失效控制原因中因开关芯片导致的失效也是逐年呈上涨的趋势,每年因开关芯片失效导致控制器失效的维修成本也在不断上升。

2020 年 7 月中国家用空调新能效标准发布,新能效实施对全球能效结构趋势的影响成为大家关注的焦点。从新实施的能效结构来看,未来新 1 级和新 3 级能效空调产品将是市场主导,尤其是新 1 级能效,预计市场占有率还将持续扩大。变频空调开关电源电路使用开关芯片在实际应运中出现多单失效,严重影响产品使用可靠性,此问题急需做多元化的分析研究解决。本文重点研究 PI 厂家开关芯片的可靠性及其失效机理,通过售后失效数据采集,对其进行专项优化整改。

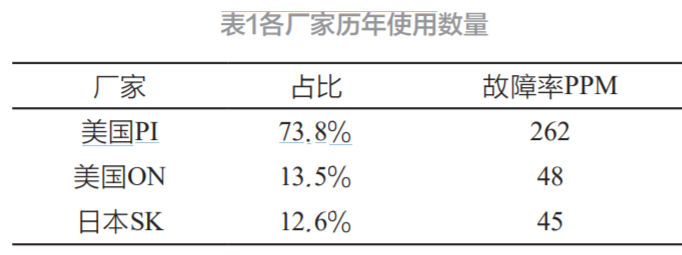

现在市场使用的主流开关芯片厂家主要有美国的 PI 与 ON(安森美),以及日本的 SK。因其三个厂家开关芯片可靠性高、电路设计成熟、应用场景范围广等特点,在开关电源电路中得到大批量使用。开关芯片从 2014 年开始不断大批量使用以来,售后失效数量也在成倍增长。统计 2019 年开关芯片售后失效数据,见下表 1,主要是 PI 厂家失效,占比总失效数 73.8%,故障率高达 262PPM。ON 与 SK 厂家失效占比较少,故障率相比来说较低,通过多个方面数据显示 PI 厂家开关芯片失效尤其突出。

统计 PI 厂家开关芯片售后失效数据,最近两年出现失效增多,已经有 300 多单,主要失效 3 脚及弱电侧对地值小或短路。具体失效统计数据见下表 2。

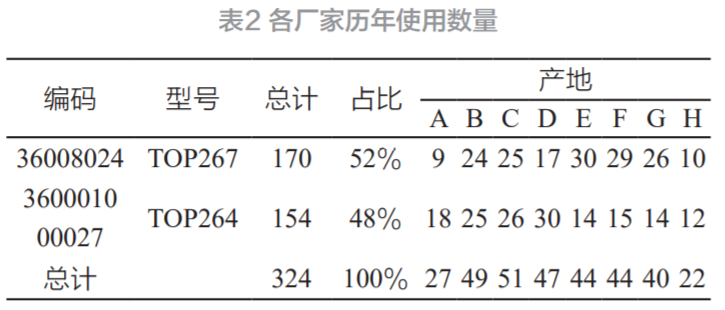

开关电源是电源模块发展的根本,是电源发展的趋势,选用功率半导体元器件作为软启动开关,利用晶体管的占空比实现电路的导通和关断,以便对输出实现在不同工作下的稳定调整输出。

开关电源电路由 DC-DC 转换器,驱动器,信号源,比较放大器,负载等组成,图 1 是它的基础结构框图。开关电源不同于普通低频变压器电源,主要是通过在初级绕组回路中串入开关管,通过高频可调占空比地开关,从而使加在初级绕组两端的 HVDC 在电路中形成脉冲变化的电流,将能量通过磁芯传至次级绕组,再通过半波整流和滤波,配合电压、电流反馈,最终形成我们所需要的低压直流电源。

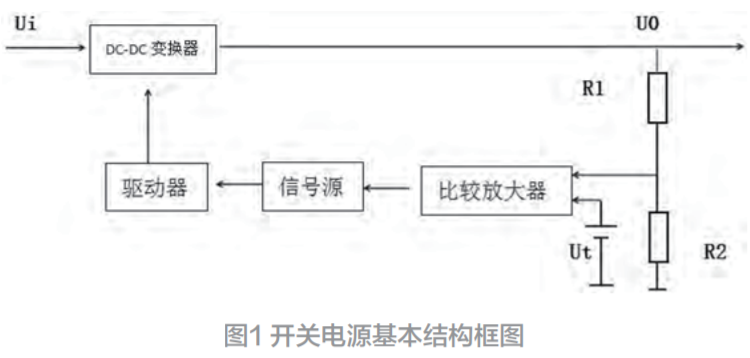

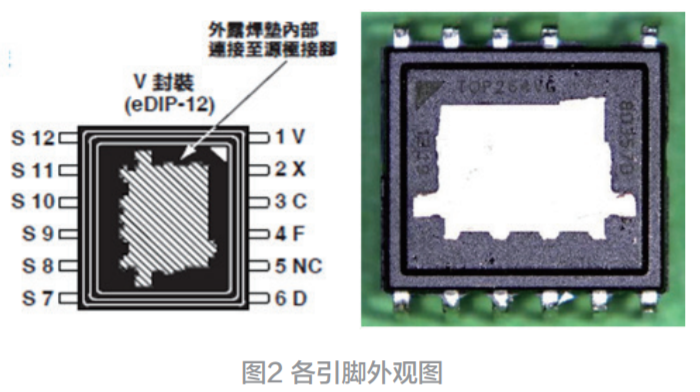

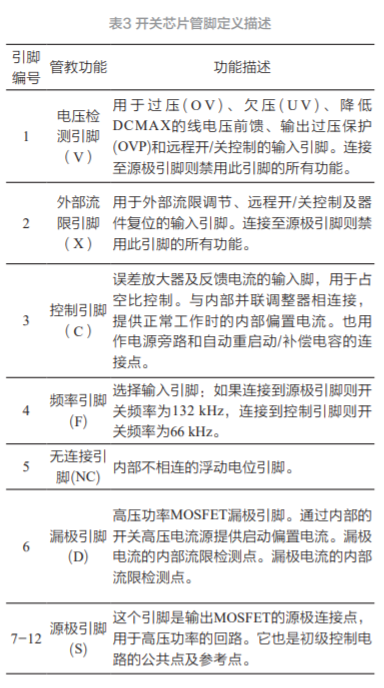

PI厂家TOP264(编码:7)与TOP267(编码:36008024)开关芯片引脚排布均相同,管脚功能描述相同,只是其功率不一样。各引脚外观图如图 2 所示。 PI 厂家 TOP264-271 系列开关芯片各管脚定义描述,见下表 3。

开关电源电路设计是一个完整的闭环电路,单个器件失效要从整个电路分析。出现开关电源芯片失效有很大的可能是芯片本身问题,或者电路设计存在问题及出现磁饱和。开关电源磁饱和与开关电源电路中器件配合有直接关系,开关电源芯片、高频变压器、输入电源、应用环境、测试过程等都是影响开关电源可靠性核心问题。一般磁饱和会导致芯片漏极产生瞬间过压冲击从而击穿 芯片,主要体现为芯片表面烧毁及炸裂,本次出现的失效模式与此不一样,针对产生疑问做多元化的分析验证。

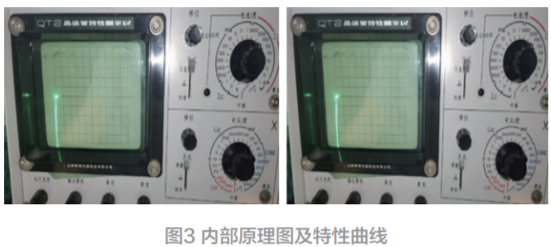

对失效主板检测芯片 3 脚对地短路,3、4 脚短路,失效主板更换芯片测试正常,芯片集中在弱电侧失效,强电侧 MOSFET 没有击穿失效及受损现象。失效样品引脚 I-V 特性曲线 脚对芯片源极短路,其余引脚特性无异常。

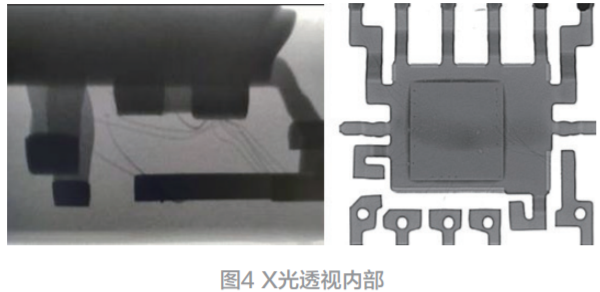

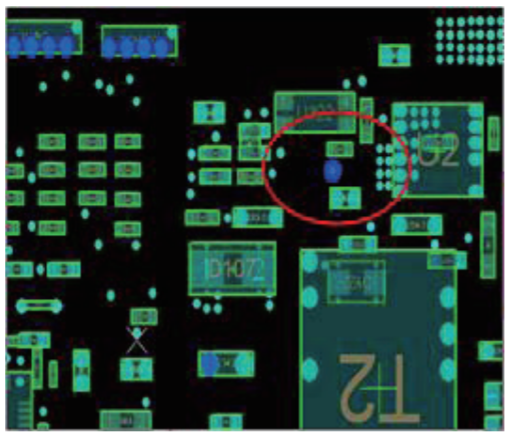

观察内部结构,见图 4,对不良品进行 X-RAY 透视显示不良品焊线正常、弧度正常,通过观察未发现结构性异常。

取其中 5 个 故障样品进行开封观察内部结构,见图 5 所示,能够正常的看到内部晶片有大面积过电烧毁的痕迹,未见产品晶元制造不良。

分析结果:对 PI 厂家失效芯片分析,确认芯片无制造不良,为过电导致内部晶片损伤。

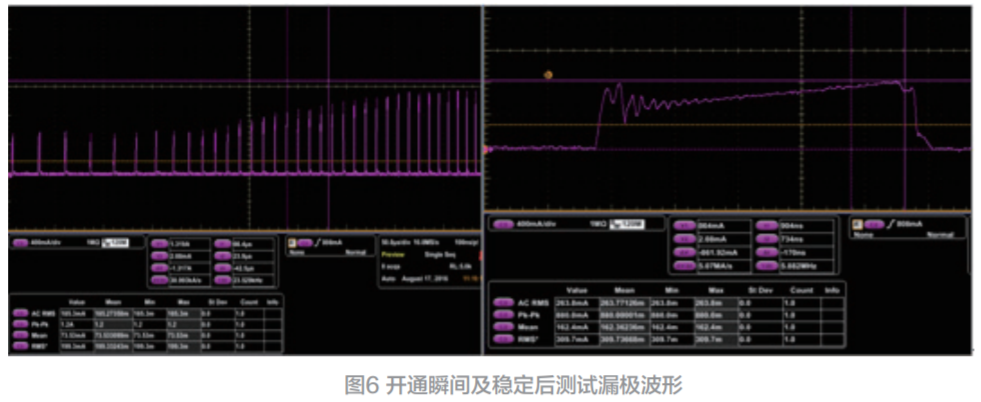

过载测试漏极瞬间开通电流峰值,通电 50 次测试最大电流峰值 1.8 A。稳定后平均电流值约 900 mA,通电 50 次测试平均电流值在 800 mA-1.2 A。测试波形如图 6 所示。

分析结果:经过对失效主板进行整机分析验证及过载波形分析测试确定电源芯片失效非磁饱和问题导致。实际开关电源漏极耐压设计余量充足。整体测试开通瞬间漏极峰值电流小于设计值 60%。

经过对芯片弱电脚进行 ESD 测试确定芯片 ESD 极限水平均超过 10 kV,综合评估非芯片 ESD 等级低。PI 厂家开关芯片售后失效分体机主板集中在 3 脚失效问题做 ESD 测试,施加最高电压 10 000 V,主板只出现芯片短暂复位,主板无失效,测试确认 ESD 放电回路设计合理,没再次出现在光耦附近有放电现象,放电是在 K1K2 继电器位置。目前厂内主要使用 36008024 TOP267VG 和 7 TOP264VG2 款开关芯片,其中 TOP267VG 型号芯片主要使用在柜内机以及商用 机主板上,TOP264VG 型号芯片主要使用在分体内机主板上,从售后失效数据看这 2 款芯片均有失效,且集中在第 3 脚,其中 TOP264VG 型号芯片失效最为突出。

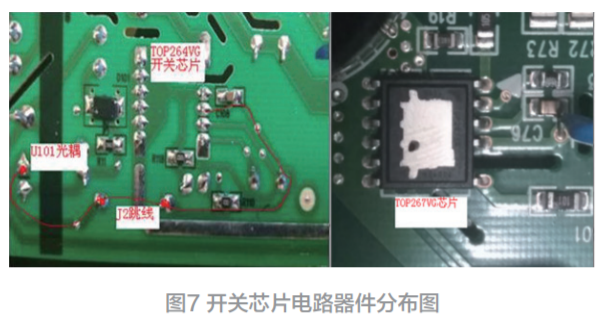

2 款芯片在电路设计上均在芯片 4 脚频率引脚 (F) 与 6 脚漏极引脚 (D) 之间开有避火槽,符合控制器设计规范,具体见图 7。对比目前班组生产分体机主板(1),开关电源芯片 TOP264VG 第 3 脚经过 J2 跳线 脚上,无防护元件,电路设计上存在缺陷。柜机主板(5)开关电源芯片第 3 脚有 C76 片状电容 104 K/50 V 防护。

从生产的全部过程排查情况看,其中 450 V/150 µF 电解电容在未使用放电板放电前残留电压较高在 3 V 左右,450 V/47 µF 电解电容残留电压较低,生产过程已均使用放电板放电后进行插装。功能自动测试均自带有放电电路,测试后电解电容残留电压低于芯片安全电压 3 V。

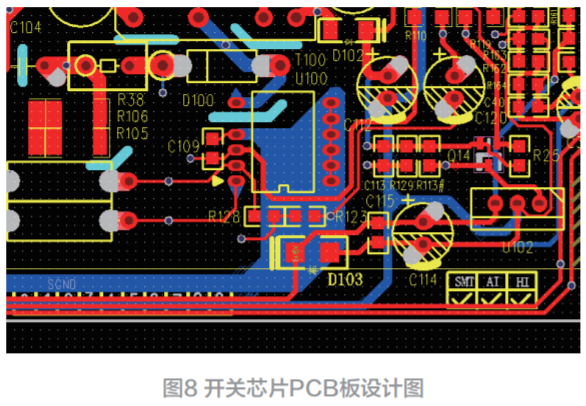

对 PCB 板设计电路核查,见图 8 所示,发现有三处点距离较短,有短路隐患,具体如下。

(1)ESD 放电回路最小间距点放电击穿问题,次级供电电路与开关芯片信号反馈电路测试点距离很近。

(3)光耦输出级短路隐患,自插光耦必须要格外注意测试不能出现 3.4 脚短路隐患,光耦输出级短路开关芯片弱电失效概率很高。

图 9 所示测试植针点分布图,经查此 3 个位置范围内未植针,不存在短路隐患。FCT 测试工装在开关电源电路上无定点,不存在探针短路导致开关电源芯片失效隐患。

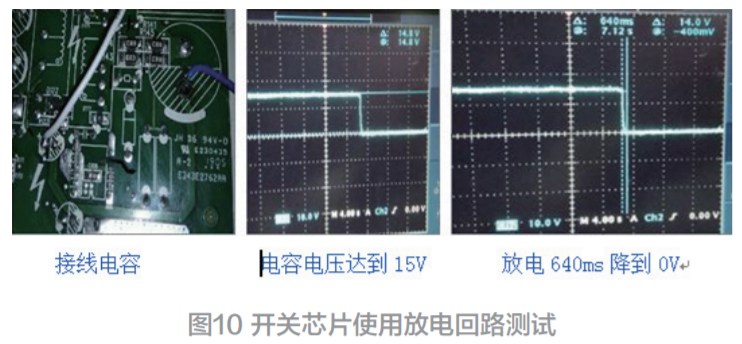

使用示波器对 5 主板 C126 电容做验证,在电容接上放电回路在 640 ms 内电压从 15 V 放到 0 V,见图 10;不接放电回路,在 17 分钟电压还有 9 V 以上(开关芯片 36008024 控制接脚电压范围:-0.3 V— 9 V),见图 11。

(1)电容两脚接上放电回路,测试完成后在640 ms 内电压从 15 V 放到 0 V。

(2)电容两脚不接自然放电,在 17 分钟还没有降到芯片的安全电压 9 V 内。

分析结果:排查测试过程测试点分布未发现明显测试点短路隐患,测试工装对控制器测试无完后,反馈光耦两端关闭,在不接放电回路情况下 C126 反馈端电解电容放电很慢,17 分钟都没下降到 9 V,电容长期带电存在很大隐患。

结论:分析开关芯片失效为过电损伤失效,非开关芯片本身异常。控制器测试完后反馈端电容不能有效放电,电容部放在流水线或是人接触等因素会导致电容放电损坏开关芯片弱电引脚,导致开关电源芯片内部晶圆软损伤。分析此次开关电源开关芯片失效为设计缺陷导致,为应用电路设计不合理,没有对电解电容有效放电。

电解电容增加放电工装,对控制器开关芯片电源电路次级输出供电光耦电路 47 µF 电容(5 主板对应是 C126)增加放电处理,见图 12,验证放电效果非常明显。此种放电影响测试效率,且放电工装与放电部点损坏短路也会导致开关芯片失效,不能有效监控,只能作为临时措施。

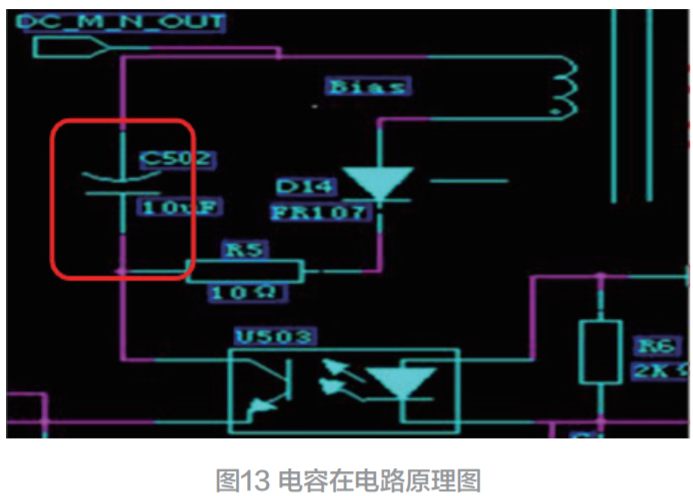

开关芯片集中在弱电侧控制端失效,弱电侧失效多数跟主板线路设计走线及过程 ESD、过程测试放电管理存在很大关系,分体机中 PI 的开关芯片电路设计存在不足,在主板测试完,光耦输出级处于开路状态,电解电容储存电量是没有负载回路进行消耗,如果过程管理不当很容易出现操作、周转等异常因素导致芯片过电损伤。依据相关电路分析,模拟在光耦供电电路 C502 电解电容(如图 13)两端并联 20 kΩ 片状电阻放电,以便能更好快速消耗电解电容储存的电量,结果显示储存电量 4 秒内时间消耗完毕,放电效果显著。

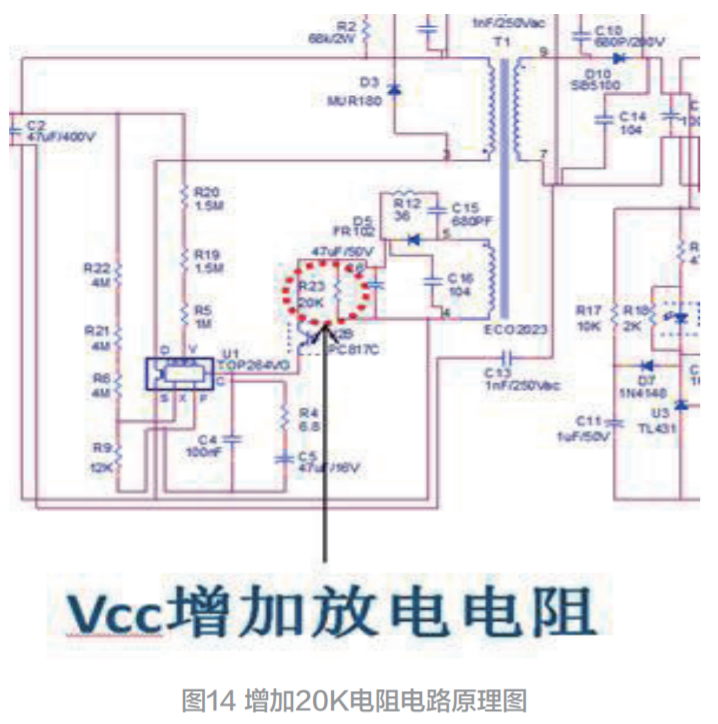

TOP264 开关芯片在光耦输出端电解电容增加 20 kΩ放电电阻,测试电容放电情况。加上 R23(20 K)放电时间约 4 秒。

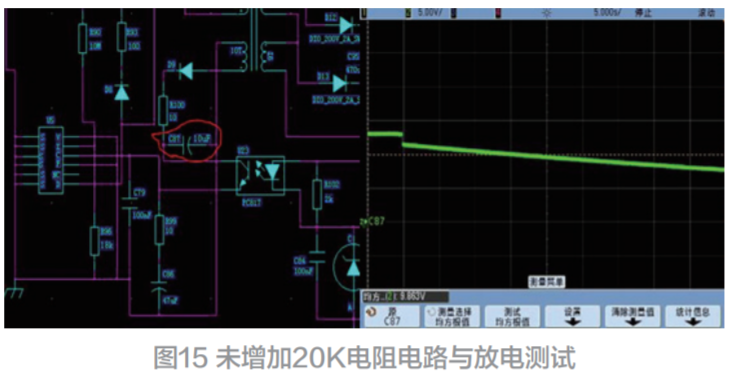

去掉电路 R23 放电电阻,2 单故障板未增加 20 kΩ 放电电阻,测试光耦输出端电解电容放电情况,放电时间超过 5 分钟,单个控制器从测试到打包完成在 2 分钟内,主板一直生产过程后工序一直带电。

由于 2019 年 PI 厂家的 TOP264 电源芯片在售后故障率较高,针对失效点大多分布在于 3 脚对地短路问题,从设计基础增加了 20 kΩ 放电电阻,整改后失效大幅度降低,但还是有失效。实际多次模拟验证过程测试完成后,测量开关芯片线 所示,测试后放电未发现异常情况。

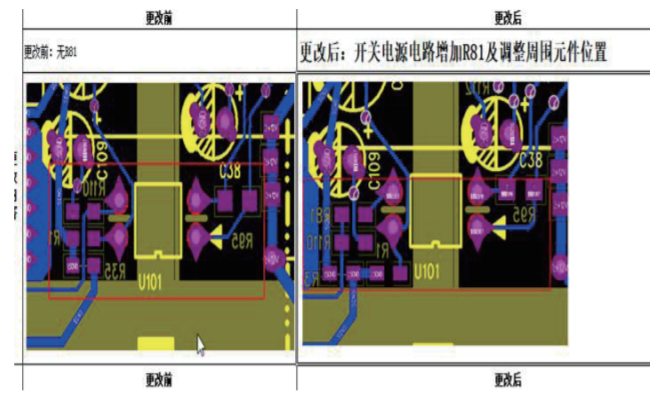

经过对电路分析研究,发现放电只是一部分,当外部有比较大的浪涌电压与出现瞬间短路放电,将直接到开关芯片 3 脚控制端,此电压短时间内有损伤 3 脚的隐患。研究之后发现在开关电源芯片 3 脚对地增加 100 Ω限流电阻(R74),见图 17 所示,可以轻松又有效起到限流作用,且可缩短放电时间。通过模拟空载上电验证,电路优化后放电时间减少到 3 秒,且当外部有浪涌电压时此电阻可以有效泄放。

本次售后出现开关芯片失效,经多方面分析验证得出非芯片本身出现异常,属于开关电源电路电路设计缺陷,在电路设计开发时未能有效考虑测试开关电源放电设计,电路设计缺陷评估不充分导致实际应用出现失效。整改通过优化电路设计,在电容端增加 20 kΩ 放电电阻,在 3 脚增加 100 Ω 放电电阻。整改后电路经过实际试验验证确定可以有效解决实际问题,实际应用效果非常明显,开关芯片失效大幅度减少。

[4] 项永金,崔斌,等.POWER开关电源芯片应用静电损伤失效可靠性研究与提升[J].电子科技类产品世界.2018(11):68-70.

下一篇:筑梦新厂 智汇伊顿